Build a 2-bit CPU

Objective of this lab:

The purpose of this lab is to learn about CPU Organization by building a simplified 1-bit CPU and 2-bit CPU.

Preparation

Read lab lecture notes.

Lab Assignments

- Create a project Lab2.circ in the Logisim.

- Add a circuit testing Registers (including 1-bit, 2-bit, 8-bit).

- Add a circuit testing TRI-STATE BUFFERS (including 1-bit, 2-bit, 8-bit).

- Add a circuit testing Decoders (including 1 to 2, 2 to 4, and 3 to 8 decoders).

- Add a circuit to build a 1-bit CPU described in the lab notes.

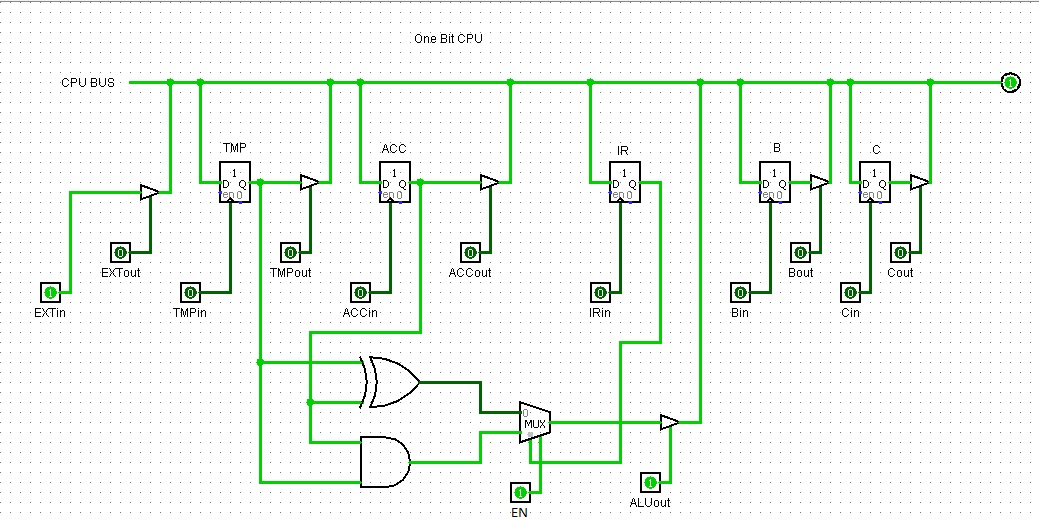

Here is a picture of the 1-bit CPU circuit for your reference.

Some Relevant Details:

The ALU performs two operations, XOR and AND.

The operation to be performed is determined by the code in the IR.

The value 0 in the IR indicates an XOR operation and the value 1 in IR indicates an AND operation.The following control signals will be required for our 1-bit CPU in this lab:

ACCout, ACCin, TMPout, TMPin, ALUout, IRin, Bout, Bin, Cout, Cin, EXTin, EXTout.

- To implement the operation AND, let's assume that

it uses the operands in registers B and C, and then stores the result in C,

The following instructions would have to be executed.

(assume the external input switch is set to the value '1' - the pre-condition for the AND operation):

Remember to pre-load '0' in register B and '1' in register C.

And see what is the result in register C.1. EXTin, EXTout, IRin. // Load '1' in register IR for AND operation. 2. EXTin, EXTout, Bin. // Load '0' in register B. 3. EXTin, EXTout, Cin. // Load '1' in register C. 4. Bout, ACCin. 5. Cout, TMPin. 6. ALUout, Cin. 7. Cout.

Practice these microinstructions with your newly built CPU. - Do the following for your lab assignment:

Write out the steps necessary to implement the operation XOR that uses the operands in the register ACC and register C, and then stores the result in register B.

- You are now able to Build a 2-bit CPU by expanding the 1-bit CPU described in the lab notes.

Remember to have a 2-bit bus for your design.

The 2-bit CPU will do the following operations: - For instruction 00, do 2-bit XOR, test 10 XOR 11 = 01

- For instruction 01, do 2-bit AND, test 10 AND 11 = 10

- For instruction 10, do 2-bit NOT operation, the Operand will be in the register ACC, test NOT 10 = 01.

- For instruction 11, do 2-bit OR, test 10 OR 11 = 11

Hand in the following:

- Submit the file Lab2.circ which includes all the circuits required. No Lab2.circ, no marks!

- Submit the file Lab2.pdf which contains the following (No Lab2.pdf, no marks!):

- Screenshot of your circuit testing Registers (including 1-bit, 2-bit, 8-bit).

- Screenshot of your circuit testing TRI-STATE BUFFERS (including 1-bit, 2-bit, 8-bit).

- Screenshot of your circuit testing Decoders (including 1 to 2, 2 to 4, and 3 to 8 decoders).

- Screenshot of the 1-bit CPU circuit that you built.

What are control signals EXTin, EXTout and Cin for?Write out the steps (micro instructions) necessary to implement the operation XOR that uses the operands in the register ACC and register C, and then stores the result in register B. Show value in B on bus. Remember to preload IR with "0", preload ACC with "1" and C with "0". - Screenshot of the 2-bit CPU circuit you built.

- The micro instructions (steps necessary) to implement the following operations described above.

Remember the pre-conditions.

- Do the XOR operation with the values in register B and C, and store the result in C. Test 10 XOR 11 = 01

- Do the AND operation with the values in register B and C, and store the result in B. Test 10 AND 11 = 10

- Do the NOT operation with the value in register C and store the result in register B. Test NOT 10 = 01

- Do the OR operation with the values in register B and TMP, and store the result in C. Test 10 OR 11 = 11

Please Note: For all above four operations, you need to preload values in the registers from the EXTin.

Use the above testing examples for your lab assignment hand-in micro instructions.